精選版 日本国語大辞典 「集積回路」の意味・読み・例文・類語

しゅうせき‐かいろシフセキクヮイロ【集積回路】

- 〘 名詞 〙 電子回路部品の一つ。トランジスタなどの能動素子を含む、複数個の部品をきわめて小さなケースに組み込んだ素子。一個のシリコン結晶で回路を構成したものをモノリシック集積回路、トランジスタのチップを印刷基板に取り付けたものをハイブリッド集積回路という。IC。

改訂新版 世界大百科事典 「集積回路」の意味・わかりやすい解説

集積回路 (しゅうせきかいろ)

integrated circuit

通常はICと略称され,〈二つ,またはそれ以上の回路素子のすべてが,一つの基板上または基板内に組み込まれている回路であり,設計から製造,試験,運用に至るまで各段階で一つの単位として取り扱われるもの〉と定義されている。ここで基板というのは,トランジスターやICがその上に形成される単結晶素材で,通常は元素半導体であるシリコンが使用されるが,高性能ICに対しては,化合物半導体であるガリウムヒ素GaAsが使用される。ICは所定のウェーハー処理工程の後,1辺が数mm~3cm程度の単位ごとの小片に切断される。これをチップchipまたはダイdieと呼ぶ。

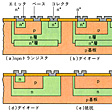

トランジスター,ダイオード,抵抗,キャパシター(静電容量)のような,電子回路を構成する要素を回路素子という。素子というのは,機能として分離できない最小単位というような意味である。トランジスターのように電力増幅や発振の能力のある素子を能動素子,ダイオードや抵抗,キャパシター等を受動素子という。トランジスターには,バイポーラー形とMOS形があり,ICにもこの2種の系統がある。

概要

ICは単純に一つの基板上または基板内に複数個の回路素子が分離不能の状態で存在しているだけのものではなく,相互に結合されて特定の機能を有するものでなければならない。また,通常電子回路は配線基板上に個々の回路部品を搭載した形で使用されるが,ICはこのように単に個々の部品を集合して相互配線したものではなく,ICに含まれる能動・受動の各素子が同時に一括して製造されることに特徴がある。

半導体ICはトランジスターの発展したもので,それを構成するすべての回路素子が1個のチップに含まれている。このことからモノリシックmonolithic(一つの結晶片でできているという意味)であるといわれる。最近ではICはLSIと呼称されることが多い。

当初ICはコンピューターの演算処理装置や記憶装置といったシステムを構成する多数の回路ブロックや部品の一つという概念であった。しかし今日では,LSIの集積度は演算処理LSIで1000万トランジスター,メモリーLSIでは10億トランジスターを超えており,LSIはそれ自体で独立したシステムに進化した。パソコンの頭脳であるマイクロプロセッサーはその典型である。LSIの出現以前はコンピューターは大型で高価な装置であり,操作にも専門家を要したが,今日ではそれ以上の性能を持つパソコンが,机上で簡単にだれにでも扱えるようになっている。また携帯電話の普及に象徴されるように,LSIは通信形態にも大きな変革をもたらした。

トランジスターの発明は科学技術史上特筆すべきイベントであるが,ICはトランジスターの優れた素質を受け継ぎ,LSI,VLSIへと進化して,社会的にも大きなインパクトを与えている。近年エレクトロニクスは日本の代表的な工業に成長した。その中核をなすICはかつて〈産業の米〉といわれたが,情報化社会の到来によりLSIはすでに米の地位を超えたといえよう。

特徴

ICの第1の特徴は,小型・軽量・低電力にある。このためIC開発の大きな原動力は軍事,特に航空・宇宙であった。ICのこの特徴は,身近なものとして電卓の発展を見れば容易に理解できる。最初に登場した電卓はトランジスター式で,現在のパソコン本体程度の大きさのまさしく〈電子式卓上計算機〉であったが,その後IC化・LSI化が進み,機能的にも高度化され,いわゆる関数電卓でも掌に乗る大きさになった。また消費電力も,小型の電池でかなり長時間使用できるほどに低減化され,最近では太陽電池を装備し室内照明で動作するものも一般化されている。ICのこのような優れた資質が人工衛星やミサイルの開発にきわめて重要な意味を持っていたのである。

第2の特徴は高性能である。コンピューターでは計算速度が速いほど一定時間内に多くの計算を行うことができるので,コンピューターの性能向上には基本構成要素である論理回路を高速化しなければならない。一般に同じ性能のトランジスターを使用して回路を設計する場合,動作速度を速くすると消費電力が大きくなる。したがってICは,単位機能当りの動作速度と消費電力の積(速度電力積という。単位はジュール)が小さいほど性能がよいことになる。消費電力の増大は電源装置に跳ね返るばかりでなく,回路の実装や機器の冷却法にも大きな影響を与える。電気信号は光速度で伝播し,真空中でも3cm進むには0.1ns(1ns=10⁻9秒)かかる。実際の回路では真空中よりも信号の伝播速度が遅い(信号伝播速度は真空中の となる)。最近の回路では1ns以下の動作速度が問題となるので,回路の物理的寸法が小さいということは,装置の性能上きわめて重要である。ICでは回路がmmからcm台のチップに入っているので回路間を信号が伝播する時間が短く,またIC内のトランジスターは小型で少ないエネルギーで動作するため,単体のトランジスターに比べて動作速度が速い。現在の高速ICでは,単位回路の動作時間は0.01ns台である。

となる)。最近の回路では1ns以下の動作速度が問題となるので,回路の物理的寸法が小さいということは,装置の性能上きわめて重要である。ICでは回路がmmからcm台のチップに入っているので回路間を信号が伝播する時間が短く,またIC内のトランジスターは小型で少ないエネルギーで動作するため,単体のトランジスターに比べて動作速度が速い。現在の高速ICでは,単位回路の動作時間は0.01ns台である。

第3の特徴は経済性である。トランジスターやICの製造工程で前処理またはウェーハー処理と呼ばれる工程は一括処理であり,本質的に量産性がある。また1チップ内の回路規模が大きくなっても製造工程数が増加するわけではないので,製造歩どまりが許される範囲内で集積度を大きくしていけば,1単位回路当り,すなわち単位機能当りの価格が,低下することになる。LSIの代表的量産品種であるMOSダイナミックメモリーの1ビット当りの劇的な価格低下動向は,この事情をよく反映している。

特徴の第4は高信頼性である。個々の部品を配線基板に搭載した電子回路では,はんだ接続が信頼性低下の大きな要因である。これに対してトランジスターやIC等の半導体部品では,能動性を生じる半導体本体部の寿命は本質的には永久的である。寿命の主要因は,半導体部と外部への引出線の接続部,および電流が流れることによる金属配線膜の劣化である。したがってICでは設計と使用状態が適正であるかぎり,高い信頼性を期待できる。

問題点

上述のごとくICには多くの利点があるが,その裏返しとしての問題もある。ICの製造は一括・連続処理であり,経済性はその量産性に由来する。したがってICは規格を標準化し量産することによってその経済性を享受しうるのである。メモリーはメガ(100万)ビットからギガ(10億)ビットと1チップ当りの回路規模が極度に増大しても,量産を前提とした汎用品種として設計できる。日本におけるLSI産業の発展はまさにDRAMの量産性によるものであった。

一方,論理LSIでは,ICの初期にはバイポーラーのTTLファミリーが標準化され成功を収めた。また高速用には小規模のECLが使用された。しかし集積度が高くなりLSIがシステムにまで進化してくると,メモリーの場合のように標準化することが困難になってくる。原理的には汎用で高性能のマイクロプロセッサーmicroprocessor unit(略してMPU)と大容量ROMがあればどんな複雑な論理処理でも実現可能であるが,MPUはプログラムで動作するシステムなので,処理速度は専用設計のLSIに劣る。したがって高機能LSIの性能向上には,そのシステムのために専用に設計され,MPUと機能を分担するLSIが必要となる。このようなLSIをASICという。この性格はメモリーの標準・汎用・量産に対して多様・専用・少量である。ゲートアレーやPLAは量産性と少量多品種化の矛盾に対する有望な解決策であるが,チップ内の回路使用率の向上等,解決すべき課題も残されている。さらに,回路規模の増大と機能の複雑化にともない,設計・検証・試験の各段階でのコスト削減と期間短縮が重要な課題となっている。そのため自動レイアウトや論理回路の自動診断,試験容易化設計等,設計業務におけるソフトの比重がますます増大している。この技術分野は設計自動化design automation(略してDA)と呼ばれる。

一方,LSIの製造工程でも,パターンの微細化と工程の高精度化にともない製造設備が大型化しつつあり,製造コスト上昇の要因となっている。コストの抑制には処理工程の自動化,標準化,省力化および最適化による歩どまりの改善等,総合技術力の向上が要求される。

LSIはクリーンルームと呼ばれるきわめて清浄度の高い室内で製造されるが,パターンが微細になるほど,空気中に存在する塵埃のごく小さなものまでが問題となる。このような微細な異物を除去するには,目のきわめて細かなフィルターが必要で,これは空気清浄設備の大型化を招く結果となる。また作業者はクリーンルーム内の最大の塵埃源であり,以前のように作業者がクリーンルーム内で直接ウェーハーを取り扱うことは,スペースと清浄度のうえから二重に不利である。そのためウェーハー処理工程を作業者から隔絶し,ウェーハーの処理と移動に必要な限られた狭い空間だけを極超清浄状態に保つような形態が必要である。

従来の主要なLSIの工程は一括処理である。しかし今後はメモリーLSIのような大規模生産形態とは別に,専用LSIの多品種少量生産への対応として,ウェーハーを1枚ずつ処理し個別に工程管理を行い,ウェーハーごとに異なる品種のLSIを製造する形態も導入されるであろう。

このようにLSIは設計のみならず製造工程の面でも自動化が要求されている。

発達の歴史

集積回路の発想

トランジスターが発明されたのは1947年12月であるが,その後シリコントランジスターの登場,プレーナー構造の発明があり,半導体技術は大きく進歩した。一方,50年代以降アメリカでは航空機搭載電子機器に対する軍の小型化の要求には峻烈(しゆんれつ)なものがあった。トランジスターは真空管に比べて大幅に小型化されたが,その能動部分は体積にして封入容器全体の1/10000以下にすぎない。このよけいな部分を少しでも取り除き,部品,配線,接続を合理化し,回路を高密度,高信頼度にする努力が行われた。

まず,トランジスター,抵抗といった回路部品をできるだけ小さく組み上げることから始まって,部品全体を同じ大きさにすることが試みられた。次に抵抗,コンデンサーの受動部品を薄膜化し,トランジスターはチップ状で回路にのせたものを重ね合わせ,相互に接続してプラスチックで固めるというマイクロモジュールmicro moduleの形に進んだ。これが60年ころである。また,回路的にはトランジスター,抵抗といった単体部品単位からNAND回路(否定論理和回路)などの機能回路単位の機器構成へと発展した。

回路を構成する部品を1個の半導体結晶内に製作するという考え方は以前からあり,すでに1952年にイギリスのダンマーG.W.A.Dummerが提唱している。しかし,このような考え方が技術的にある程度可能となったのは,不純物拡散によって均一に広い面積のp-n接合ができるようになった59年ころである。今日のICの歴史はこのころから始まった。59年にテキサス・インスツルメント社のキルビーJ.S.KilbyがICの基本特許を出願した。この年同社は初めて〈solid circuit〉という名称で,また60年にはウェスティングハウス社が〈molecular electronics〉としてともに現在のICの原型ともいうべきものを発表している。

バイポーラー・プレーナーICの出現

同一半導体基板中で回路を構成することのもっとも大きな問題は,回路を構成する各回路素子を電気的に分離することである。上記のテキサス・インスツルメント社のICは,この素子分離にメサエッチングを使用していた。ほんとうのICの時代はプレーナー技術の開発から始まったといえる。プレーナー技術こそは,シリコンの優れた性質をICへ発展させた鍵であった。トランジスターでプレーナー技術を開発したフェアチャイルド社は,直ちにICへの応用を開始し,以後両社はIC産業において先導的役割を果たしてきた。

MOS ICの発達

一方,半導体の表面物性に関する研究は長い歴史があり,1939年には,ショットキーW.Schottky(1886-1976)の表面障壁の理論が出され,今日でもショットキーバリアSchottky barrierとしてLSIに利用されている。また,1935年にはヘイルO.Heilが現在のMOSトランジスター(MOSはmetal oxide semiconductorの略で,金属と半導体の間にケイ素酸化物などの薄い絶縁層をはさんで作ったトランジスター)の基本的特許を出願している。しかし,これが実用になるには,良好な表面状態を実現できる技術が確立されるまでの約30年間を必要としたのである。シリコンを処理する技術がほぼ確立された65年ころから単体のMOSトランジスターが製造され,しだいにMOS ICへと発展していった。当初,MOS ICは,バイポーラーICに比べて動作速度は遅いが製造工程が簡単であることや集積度を大きくできることなどから,シフトレジスターやメモリーとして実用化された。その後電卓や時計などのICとして著しい技術の進展を見,70年に1キロビットのMOSダイナミックメモリーICが出現して,それ以来MOS技術はVLSIの先端を開くパイオニアとなった。

集積回路の限界

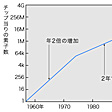

集積回路技術の進歩の指標として集積度と最小線幅がある。集積度が大きいほど,1チップに多くの素子を入れることができる。またICパターンの最小線幅が小さいほど同じ素子数のICを小さな面積で実現できる。MOS LSIの場合,集積度はほぼ4倍/3年のペースで上昇しており,また最小線幅は4年でほぼ1/2になっている。

MOS ICには,素子の幾何学的寸法を1/kにすると性能(1/速度電力積)がk3倍になるというスケールダウン則がある。これは集積度の増大と性能の向上とが矛盾しないということであり,小さいことはよいことなのである。VLSIの技術が微細化を指向する理由はここにある。

微細化を進めていくとパターン幅が大きかった場合にはあまり表に現れなかった現象がしだいに大きな障害となってきて,単純なスケールダウン則どおり事が運ばなくなる。すなわち,製造技術上,それ以上微細化が困難となる点,または微細化しても性能が向上しなくなる点がVLSIの限界である。前者については現在最小パターン幅が200Å程度であるが,膜厚では数十Åまで可能となっているので,最終的にパターン幅も数十Å程度までは可能であろう。また後者については多くの研究があるが,単純に考えると次のようになる。すなわち,現在のトランジスターはバイポーラー,MOSともにp-n接合を使用しているが,p型半導体,n型半導体がそれぞれp型,n型の性質をもつためには,その中を走る荷電粒子が少なくとも30個程度の不純物原子に遭遇しなければならないと考えられる。一方,シリコンの中に入りうる不純物原子数は最大1020/cm3の程度であるから,最小のp型またはn型領域の大きさは一次元で30/3\(\sqrt{1020}\)cm≅600Åの程度であろう。

従来,LSIに関する将来予想は,多くの場合的中しなかった。実際の進歩が予想を上回るのである。技術予測は,単なる占いではなくその時点における最新技術に立脚した理論的なデータをベースとしているので,その時点で考えられる以上の革新的新技術が開発されれば,予測ははずれることになるのである。動作原理や構造が新しいトランジスターが開発されれば,微細化の展望はさらに開けるのである。現在VLSIに関する将来予測は少なくないが,今後も現実が予想を上回るであろう。

材料

現在のICはそのほとんどがシリコンで,ガリウムヒ素はきわめて少ない。ガリウムヒ素はスーパーコンピューターや超高速通信用として期待されているが,将来ともICの約80%はシリコンが残ると考えられている。したがってここではシリコンIC,なかでも現在最も一般的なMOS ICについて説明する。

シリコンの単結晶は,きわめて高純度の石英から精製された多結晶シリコン原料をるつぼ中で溶融し,これに種結晶を浸して回転させながら徐々に引き上げる方法で製作される。これを薄く輪切りにした円板上の単結晶をウェーハーといい,ICの出発点となる材料である。ウェーハーの表面は,機械的な研磨と化学薬品による処理によってきわめて平坦で清浄な鏡面に仕上げられる。一般的なシリコンウェーハーは厚さが0.5mm~1cm,直径が200mm~250mm(8~10インチ)で,円周の一部に方向を示すための直線状の切り欠けがある。

製法

ICの基本的な製造工程は次のように分類できる。(1)ウェーハー表面に特定の種類の薄膜を形成すること。これには,酸化,化学的膜形成,蒸着,スパッターリングなどの方法がある。(2)特定の種類のガス雰囲気中で高温状態にすること。これを熱処理という。通常は窒素と水素が用いられる。石英管中にウェーハーを入れ,外部から電熱線,または赤外線ランプで加熱する。今後はレーザービームでウェーハー上の特定の領域のみを選択的に走査して加熱するレーザービームアニールが多く用いられよう。(3)特定の種類の元素をウェーハー,または表面の膜中に導入すること。これにはイオン注入と拡散がある。この元素はシリコンに対して異種なので,不純物といわれる。通常はリンP,またはヒ素As,ホウ素Bが用いられる。(4)パターンを形成すること。電子回路のパターンを作る。(5)特定の種類の表面の膜を除去すること。これをエッチング,または剝離という。(6)表面を洗浄,乾燥すること。

ICのウェーハーは,この基本処理工程の繰返しによって表面に回路が形成されていく。最後にこのウェーハーは四角いチップに切断され,容器に封入されて完成品となるが,ウェーハーの形状で行われる製造工程をウェーハー処理工程,または前工程といい,チップ切断以後を組立工程,または後工程という。以下,上記工程におけるおもなものの概要を説明しよう。

酸化

酸化はシリコンウェーハーを高温の電気炉に入れ,酸素ガスを流すと,シリコンの表面でSi+O2─→SiO2の反応が起こり,二酸化ケイ素SiO2が形成される過程である。このSiO2は石英と同じ物質で耐熱性があり化学的にも強く,不純物原子を通さないという優れた性質があり,ICではきわめて重要な働きをする。ゲルマニウムGeの時代にはICは出現せず,シリコンの時代になってICが登場したのはSiO2のこのような性質によるものである。

今日までに開発されてきたICウェーハープロセスの中で,きわめて重要な技術に選択酸化がある。これはウェーハー全面に酸化膜を形成するのではなく,ウェーハー表面の特定領域を選択的に酸化するもので,バイポーラーICのプロセスにも広く用いられている。ウェーハー表面にシリコン窒化膜Si3N4を形成し,酸化膜を成長させたい部分の窒化膜を後述のフォトエッチングによって除去し酸化する。窒化膜がある部分は酸化されない。この方法で作った酸化膜は,その厚さの約半分がシリコン基板の内部に埋め込まれた形となるため,表面段差が約半分となり,段差越えの配線の歩留りが向上する。また二つのトランジスターの間隔を狭めることができる。しかしVLSIではこの技術でも不十分になってきており,酸化膜をほぼ完全に基板の中に埋め込む新しい技術が開発されている。

化学的膜形成chemical vapor deposition

略してCVD。原料元素を含む気体化合物を特定の温度に保ったウェーハー周囲に流し,化学変化によってウェーハー上で微粒子状の固体物質を析出,沈着させ,堆積により膜を形成する方法である。通常はシランガスSiH4を原料とし,多結晶シリコン膜の場合には分解で,シリコン酸化膜の場合には酸素との反応で,またシリコン窒化膜の場合にはアンモニアガスとの反応により析出させる。最近は低い反応温度で膜形成を行う方法が開発され,ガス放電や紫外線で反応を促進させるプラズマCVDや光CVDが実用化されつつある。

蒸着

高真空中で,材料となる金属を電子線照射によって加熱し蒸発させ,ウェーハー表面に付着させて金属膜を形成する。

スパッタリングsputtering

低圧のアルゴンガス中で放電を起こさせると,中性アルゴン原子は正電荷をもつアルゴンイオンと電子に解離する。イオンは電界によって加速されて陰極に衝突し,その運動エネルギーで陰極から原子をたたき出す。この原子を陰極に対向して設置したウェーハーに付着させ,表面に陰極物質の膜を形成する。蒸発しにくく蒸着が困難な物質や,合金で蒸着では組成が変化するような場合に使用される。ICではシリコンを微量混入したアルミニウムの膜形成に用いられている。

イオン注入

シリコン結晶に不純物原子を導入し,特定の領域をn型またはp型にする方法は,トランジスターの時代からもっとも基本的なウェーハープロセスの一つであった。この目的で現在もっとも広く用いられているのがイオン注入である。対象とする不純物原子をイオン化し,20~200kVの電圧で加速してウェーハーに衝突させる。イオンの運動エネルギーが小さい場合にはスパッターのように衝突したイオンが原子をたたき出すが,エネルギーが大きくなると衝突したイオンは物質中に侵入し,物質原子と衝突を繰り返してエネルギーを失い,やがて表面からある深さで停止する。イオンの加速電圧とイオン電流密度によって,ウェーハーの表面からの深さと不純物濃度を制御することができる。

ウェーハー表面をある種の膜で遮り,この膜の厚さを加速されたイオンが通り抜けられない程度に十分厚くしておく。イオンを阻止するのに必要な厚さは,膜物質の種類と注入イオンの種類により,加速エネルギーの関数として求められている。後述するパターン形成の手法により,イオン注入をしたい部分の膜を除去してイオン注入を行う。パターン形成した表面の膜は,イオン注入に対するマスクとなる。このマスクには二酸化シリコンSiO2,窒化シリコンSiN4,アルミニウムAlの蒸着膜および後述のフォトレジストが用いられる。このような方法で,例えばp型シリコン基板にリンP,またはヒ素Asのイオンを注入してn型領域を形成し,ここをp-n接合とすることができる。

将来十分な電流密度をもち高精度で偏向できるイオンビームの注入装置が開発されれば,マスクレスイオン注入が可能となる。

パターン形成

チップ内にトランジスターや配線を作り込むためには,まずそれら各要素の領域を規定する幾何学的パターンを形成する必要がある。単体トランジスターからIC,LSI,VLSIへと進むにつれてパターンは微細化,複雑化してきており,パターン形成技術の重要性はますます大きくなっている。

現在もっとも一般的なパターン形成方法はマスクパターンの転写である。マスクはきわめて平面度のよい四角いガラス板の全面にクロムなどの金属薄膜を蒸着し,不要な部分の膜をエッチングにより除去したものである。マスクパターンは,電子線描画装置で作成される。この装置は電子顕微鏡に似ていて,電子を集束加速して電子ビームを作り,これを偏向電極で偏向して特定の位置に照射するものである。マスクとなるガラス板の金属蒸着薄膜の表面に感光性物質の膜を塗布する。この物質をフォトレジストという。フォトレジストは本来は紫外線に対して感光する高分子物質で,光のエネルギーにより露光部の分子状態が変化し,特定の現像液に対して可溶性,または不溶性となるものである。前者をポジ形レジスト,後者をネガ形レジストという。電子ビームでパターンを形成する場合には,電子ビームの照射に対してよい感光特性をもつレジスト材料を使用しなければならない。

フォトレジスト膜を塗布したウェーハーにマスクパターンを転写する方法には,マスクをウェーハー上に直接密着させるコンタクト式,マスクとウェーハーを離して平行に置きマスク上のパターンをウェーハーに光学的に投影するプロジェクション式,マスクパターンを1/5,または1/10に縮小して1チップごと投影していくステッパー式があるが,LSIではステッパー式である。転写にはいずれも紫外線が使用されるが,使用する光の波長が短いほど精度がよいので,最近はX線露光装置が開発されている。

感光したフォトレジスト膜を現像してパターンを得るが,マスクパターンとの転写誤差が少ないことがLSIの歩留り上重要である。ウェーハープロセスではこのパターン形成は何回も繰り返される。したがって2回目以降のパターン形成工程では,その工程までに形成されたウェーハー表面上のパターンにうまく位置合せをすることが必要である。この誤差が大きいと多色印刷の色ずれのようにパターンずれが起こる。しかし位置合せ誤差を完全に0とすることは不可能であり,可能なかぎり自己整合化を行って,高精度な位置合せを要する工程数を減らすことが重要である。自己整合は,前の工程で形成されたパターンを利用して,次の工程におけるパターン形成を高精度の位置合せなしで行う方法である。これはシリコンゲートプロセスで最初に提案された思想で,現在ではLSIプロセス設計の基本の一つとなっている。この考え方を,緑色の地に青色の円形を描く場合の例で説明しよう。薄い箔を円形に切り抜き,この片面に青色の塗料を塗ってその面を下にして白い紙にのせる。この紙全体を緑色の塗料で塗り,箔をはがすと箔に塗った青色塗料が下地について,緑色の地に青色の円が現れることになる。この際,箔の厚さが十分薄く,塗料の紙への浸込みがなければ,原理的に色ずれは起こらず,円の周辺部に白い空隙(くうげき)部や色が重なって黄色になる部分はまったく生じないはずである。これが自己整合の考え方である。

エッチング

本来は金属表面を化学薬品で腐食させることであるが,ICでは,パターン転写後に薄膜の不要部分を除去することおよびあるプロセスで使用した薄膜をその後の工程のために全面的に除去することをいう。従来はもっぱら液体の薬品(フッ酸,塩酸,硝酸,硫酸など)を使用するウェットエッチングであったが,最近はガス(CF4など)放電による活性基でエッチングするドライエッチングが多く用いられている。

フォトエッチングと呼ばれるプロセスは,露光,現像によってパターン形成したフォトレジストをマスクとしてその下地をエッチングする方法である。例えばエッチングしたい膜がSiO2であれば,フォトレジスト膜はSiO2のエッチング液に対して十分な耐腐食性をもたなければならない。またエッチング中にフォトレジスト膜がSiO2の表面から浮き上がったり,フォトレジスト膜とSiO2の間にエッチング液が浸み込んだりするとパターン崩れを起こし,SiO2の良好なパターン形成ができない。したがってマスク物質の選定は重要であり,フォトレジストをマスクとして第1の膜をパターニングし,フォトレジストを除去して第1の膜をマスクとして第2の膜をエッチングするという方法もしばしば用いられる。

ウェットエッチングは,一般的には表面に平行な方向と深さ方向のエッチング速度が等しい等方性エッチングである。したがって仕上り寸法は膜厚分だけマスク寸法とずれるわけで,これをパターン変換差という。これに対してドライエッチングでは,表面に平行なエッチングはほとんど進行せず,深さ方向のみエッチングする異方性エッチングが容易である。したがってパターン変換差をほとんど0にでき微細加工が可能なので,LSIの重要な技術の一つである。

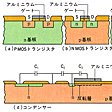

構造

現在のLSIの中で代表的なC-MOSの構造を説明する。C-MOSは相補形complementary MOS集積回路の略で,一つの回路の中にn型とp型のMOS FET(MOS field effect transister。MOS型の電界効果トランジスター)を使用し,性能のよい回路を実現するものである。C-MOSの基本回路は両FETを対とする反転回路で,両FETは電源に対して直列に接続されている。一方のFETが導通状態(ON)のとき,他方が遮断状態(OFF)となるので,定常状態では電流が流れず,わずかな(10⁻12A程度の)漏れ電流が流れているだけである。二つの状態の遷移時にパルス状の電流が流れるだけなので,消費電力がきわめて少ない。このためC-MOSは時計や電卓など電池使用の民生機器用ICとして発展した。C-MOSにはpウェル型とnウェル型とがあるが,ここでは一般的なpウェル型ついて説明する。

この形のC-MOSではn型基板を使用し,p-FETは直接基板上に,n-FETはウェルwellと呼ばれる深いp型拡散領域内に作られる。まずn型基板を酸化し,表面にイオン注入のマスクとなる酸化膜を形成する。次にフォトエッチングによってウェルとなる領域の酸化膜を除去し,ホウ素イオンを注入し,高温の熱処理を行ってホウ素原子を結晶内部へ深く拡散させてp-ウェルを形成する。

次に隣接するMOS FETの間を電気的に分離するため,MOS FETとなる部分以外の領域(フィールドという)に,選択酸化法によって厚い酸化膜(フィールド酸化膜)を形成する。次にMOSFETとなる部分にゲート絶縁膜となる薄い酸化膜を形成する。これはMOS ICの特性に重要な影響をもつ工程である。次に上述のCVDプロセスによりシリコンの多結晶をウェーハー全面に堆積させ,フォトエッチングによってゲート電極となる部分以外を除去する。n型MOS FETとなる部分をアルミニウム蒸着層で覆い,ホウ素のイオン注入を行うと,多結晶ポリシリコン層とアルミニウム層のない部分にだけホウ素イオンが打ち込まれ,p型MOS FETのソースおよびドレーン領域ができる。すなわち多結晶シリコンゲートをマスクとしてソースおよびドレーン領域を自己整合的に形成するので,その端はちょうどゲートの端と一致することになる。同様にp型MOS FET部をアルミニウムで覆い,リンまたはヒ素をイオン注入してn型MOS FETのソース・ドレーン領域を形成する。次に全面にシリコン酸化膜をCVDでつけ,ソース,ドレーンおよびゲートの電気的接続個所に穴をあける。これをコンタクトホールという。この上にアルミニウムを蒸着,またはスパッターでつけて配線に必要な部分以外をフォトエッチングで除去する。これで各MOS FETはアルミニウムの配線で接線され,回路が構成されたわけである。接続抵抗を下げるため熱処理を行い,チップに切断して容器に入れればICが完成する。

以上,きわめて簡略にC-MOS ICの原理的な構造を説明したが,実際のICでは,MOS FET相互の干渉を避けるためにフィールド酸化膜の下側にイオン注入を行ったり(チャンネルストッパーという),MOS FETの特性を改善するためゲート下側の基板表面にイオン注入をしたり(チャンネルドープという)する。また金属配線も最近では3層のものがある。

集積回路のコラム・用語解説

【集積回路用語】

- SSI

- small scale integrated circuitの略で,小規模集積回路ともいう。回路素子数が少ないICをいう。一般的には素子数100未満である。

- MSI

- medium scale integrated circuitの略で,中規模集積回路ともいう。回路素子数が中程度のICをいう。一般的には素子数100以上1000未満のものを指す。

- LSI

- large scale integrated circuitの略で,大規模集積回路ともいう。ICの中で回路素子数の多いものをLSIという。以前は1000回路素子以上のものをLSIと呼んでいたが,最近ではトランジスターが10万個以上のものをVLSI(超LSI.very large scale integrated circuitの略)というようになり,それに伴ってVLSI未満のものはLSIと呼ばれるようになった。しかしこの分類には厳密な定義があるわけではなく,10万回路素子以上のもの,10万ゲート以上のものなど,さまざまである。1982年現在,実用化されているLSIは64キロビットのダイナミックランダムアクセスメモリー(RAM)であるが,これは約7万個のMOSトランジスターとほぼ同数のコンデンサーを含んでおり,回路素子数としては10万個を超える。しかし通常はVLSIではなく,“VLSIの入口”と呼ばれている。最近の実用的VLSIは64キロビットスタティックRAMおよび256キロビットダイナミックRAMで,1メガビットのものも開発されつつある。

- ECL

- emitter coupled logic circuitの略で,エミッター結合論理回路ともいう。TTLと並ぶバイポーラートランジスターの代表的論理回路。エミッターで結合されたトランジスター間での電流切替えを,〈0〉〈1〉の論理状態に対応させて論理演算機能を行うので,以前は電流切替形論理回路(CML.current mode logicの略)とも呼ばれた。トランジスターはつねに非飽和状態(コレクター電流がエミッター電流に比例する状態)であり,このため動作速度はシリコンICの中でもっとも速く,大型コンピューターの論理回路として使用されている。しかしつねにいずれか一方のトランジスターに電流が流れているので,消費電力が大きいのが欠点である。回路機能はORおよびNORである通常コレクター側を接地し,エミッター側に-5.2Vの電源を用いる。信号レベルは低レベル-1.55V,高レベル-0.75Vである。このECLとC-MOS論理回路がもっとも代表的なICの論理回路形式である。

- TTL

- transistor-transistor logic circuitの略で,トランジスタートランジスター論理回路ともいう。マルチエミッタートランジスター(一つのトランジスターの中にベース領域を共通とする複数個のエミッターを有するもの)に論理機能をもたせ,エミッター接地インバーターとエミッターホロワーを直列に接続したシングルエンデッドプッシュプル形の出力回路を有する飽和論理回路である。バイポーラーICの標準的論理回路として長い歴史があり,ショットキーバリアダイオードを用いて動作速度を速くしたSTTLは代表的な論理回路である。回路機能はNANDである。電源電圧は+5Vを使用し,信号レベルは低レベル0.4V,高レベル2.4Vである。近年はTTLもしだいにC-MOS化されつつあり,いずれバイポーラー論理回路は高速のECLのみとなると予想されている。

- I2L

- integrated injection logicのことで,アイスクエアエルと読む。MOS ICに対抗するために開発されたバイポーラーICの一種で,1972年にIBM社とフィリップス社から独立に発表された。MOS IC並みの高密度と製造工程(バイポーラーよりも工程が少ない)によってMOSより低電圧で動作し,負荷駆動力の大きいICの実現をねらいとしたものである。縦型(基板の表面から内側に向かってエミッター,ベース,コレクターが配置されたもの)のマルチコレクターn-p-nトランジスターをエミッター接地でインバーターとして使用し,ベース接地の横型(基板の表面に平行にエミッターベース,コレクターが配置されたもの)p-n-pトランジスターを定電流源の能動負荷として使用する。回路はオープンコレクターのマルチインバーターであり,ワイヤードORが可能である。性能はバイポーラーとMOSの中間で,アナログ回路とディジタル回路を同一チップに入れる場合によく使用される。最近はMOSの性能が向上し,I2Lはしだいにその適用領域が狭められており,やがては過去のものとなると思われる。

- ファンアウト fan out

- 論理回路の一つの出力端子に並列に接続される次段の論理回路の個数。接続可能な最大数を最大ファンアウトといい,駆動能力の大きさを表す。前段と後段は同じ種類の論理回路とする。

- ファンイン fan in

- 一つの論理回路に接続される前段の論理回路の個数。例えば2個の入力端子を有する論理回路で,一方の入力端子に並列にm個の回路が接続されていて(ワイヤードORの場合),他方の入力端子には1個の回路が接続されている場合には,ファンインはm+1である。前段と後段は同じ種類の論理回路である。通常の論理回路はワイヤードORの機能がないので,ファンインは入力端子の数である。

- マスタースライス master slice

- ICは同一品種を大量生産するのが経済的であるが,LSI化が進み1チップの回路機能が複雑化してくると,少量多品種が要求される場合が多くなる。このような場合に各品種をすべて最初から別のLSIとして設計,製造するのはコスト的に不利である。この対策として,配線以外は同じLSIを作り,必要な機能に応じて配線パターンのみを変更して多くの品種を作ることが考えられた。この配線以外共通のウェーハーをマスタースライスという。特定品種についてみると,そのチップ内のある部分の回路要素は使用されておらず,他の品種では使用されない部分が異なっている。このように多少のむだはあっても,少量多品種ではこのほうが経済的である。マスタースライスでは通常,回路要素はゲート回路であり,これがアレイ状に配置されているのでゲートアレイとも呼ばれる。

- スイッチング時間

- ディジタル回路で,完全な矩形波入力に対して出力波形が上昇する場合,出力波形の最大値を100%として,入力レベルの変化点から出力波形の10%までの時間を遅延時間delay time,10%から90%までの時間を立上り時間rise timeという。また入力レベルの変化点から出力波形の50%までの時間を立上り伝播遅延時間という。これと反対に出力波形が下降する場合,入力レベルの変化点から出力波形の90%までの時間は遅延時間で,90%から10%までの時間を立下り時間fall timeという。また入力レベルの変化点から出力波形の50%までの時間を立下り伝播遅延時間という。立上り伝播遅延時間と立下り伝播遅延時間の平均を伝播遅延時間propagation delay timeという。

- 雑音余裕度 noise margin

- スイッチング回路の入力レベルに許容される雑音の大きさで,回路の入力レベルと閾値の差で表される。低レベル側と高レベル側とがある。

執筆者:吉村 久秉

出典 株式会社平凡社「改訂新版 世界大百科事典」改訂新版 世界大百科事典について 情報

日本大百科全書(ニッポニカ) 「集積回路」の意味・わかりやすい解説

集積回路

しゅうせきかいろ

integrated circuit

電子回路の一種で、トランジスタ、ダイオード、抵抗、コンデンサーなど、多くの回路素子を一つの基板上、または基板中に集積し、これらの素子間を基板表面に接した配線で接続して高密度回路構造としたもの。ICと略称でいわれることが多い。

[右高正俊]

主要分類

集積回路は製造工程と機能とによって膜IC、半導体IC、および以上二つを組み合わせた混成(ハイブリッド)ICに分類できる。膜ICは回路素子を絶縁物薄片基板上に平面的につくり、配線はその上に金属膜を重ねて形成する。抵抗やコンデンサーの相互配線の導体パターンをつくる膜の構造、ならびに製造方法によって薄膜と厚膜との二つに分類される。前者は通常0.1マイクロメートル以下の主として金属薄膜でパターンをつくるが、後者は10マイクロメートル程度の厚さのパターンを、ペースト状にした材料をスクリーン印刷してつくる。薄膜はフォトエッチングで細かいパターンが得られ、集積度は高くなるが、工程が複雑なうえ表面の平坦(へいたん)な基板を用いる必要から、許容消費電力が低くなる。厚膜ICはパターンが印刷によっているので、工程は簡単であるが、精度に限界があって集積度は高くない。これら膜ICではトランジスタ、半導体ICなどの能動素子をつくることができないので、能動素子を実装し、コンデンサー、抵抗などの受動素子を含んだ回路とした膜と組み合わせたものが混成ICである。

半導体基板中には能動、受動のすべての回路素子をつくることができるので、これらを基板中につくり込み、それらの間を基板中または基板表面に接した配線で接続したものが半導体ICまたはモノリシックIC(モノリシックmonolithicはギリシア語で単体の石の意)である。半導体ICは、すべての必要な回路素子を含んだ完全な電子回路をつくることができるので、他のICに比べてきわめて広範囲に使われている。そのため、一般に集積回路というときは、半導体ICをさすことが多い。

半導体ICはIC内で用いるトランジスタの種類によって区別される。バイポーラIC(双極性集積回路)、MOS(モス)・IC(MOSはmetal oxide semiconductorの略称、金属酸化膜半導体)と、半導体内のキャリア(電荷担体)の特異なふるまいを利用した電荷結合素子(CCD)などに分かれる。バイポーラICではnpnトランジスタを主として、2種のトランジスタを混用することが多い。MOS・ICでは1種類のトランジスタだけを用いたものと、2種のトランジスタを用いたものがある。前者には正孔を利用するトランジスタだけを用いたPMOS・IC、電子を利用するトランジスタだけを用いたNMOS・ICがある。後者には両トランジスタを対として用いたCMOS・ICがあり、1980年代以降のIC、とくにデジタル用では、電力消費の少ない後者がもっぱら使われている。

半導体ICは、すべてリソグラフィー技術を用い、微細なパターンを一つの半導体薄片(チップ)上に形成する。この場合、回路素子をつくるパターンを微細にするほど1チップ上に多くの回路素子をつくること、すなわち高集積化することができる。集積度は、記憶回路用ICでは1チップ当りのビット数で、論理回路用ICではゲート数で表すことができる。記憶回路ICでは1キロビット(論理回路では100ゲートに相当)以上100キロビット(論理回路では10キロゲートに相当)までを大規模集積回路あるいはLSI(large scale integrated circuitの略)といい、それ以上10メガビット(論理回路では1メガゲートに相当)までを超LSI(VLSI、very large scale integrated circuitの略)といい、それ以上を超超LSI(ULSI、ultra large scale integrated circuitの略)とよんでいる。

[右高正俊]

歴史

集積回路は、主としてアメリカにおける宇宙用・軍事用機器の電子回路の小型・軽量化が動機となって開発された。小型・軽量化には、小さな部品を高密度で組み立てる必要があり、このために全回路を分離しやすい部分に分け、それぞれを標準化した形状の基板上に組み立てることが行われた。しかしこの方法では、抵抗などの回路部品と基板とを別々につくって組み立てるために、小型・軽量化はもちろん量産化にも限界があった。この限界を破るため、絶縁基板上につけた膜を加工し、抵抗や配線などをつくる膜ICが、さらに膜ICの配線上にトランジスタやダイオードなどを取り付けたハイブリッドICが、第二次世界大戦の終了直後から1960年の間に開発され完成された。

一方、半導体によって抵抗だけでなく、トランジスタやダイオードなども製造できるようになった。このため、トランジスタの発明から5年後の1952年にイギリスで半導体ICの出現が予言され、1959年アメリカのテキサス・インスツルメンツ社によって試作された。このようにして生まれた半導体ICは、最初、集積化するための制限から、回路の最適化設計がむずかしく、製造条件の厳しさから歩留りが低かった。したがって価格は著しく高くなったが、価格より性能を重視する軍事用、宇宙用の電子機器にまず採用された。のち、回路と製造プロセスが改良されて歩留りが上がると、一括多量生産により価格が下がって新しい需要が次々と生まれるようになった。

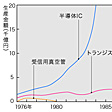

日本ではアメリカのような宇宙開発や軍用への需要はほとんどなく、経済性を重視する民需に頼っていたので、本格的にICの生産に取り組んだ1966年(昭和41)ころから1970年ころまでは、各社とも赤字に悩まされて生産は伸びなかった。日本で集積回路普及の端緒となったのは、電卓(電子式卓上計算機)とテレビジョン受像機への採用である。前者用は1969年、後者用は1972年ころから生産が順調に伸び、1975年には、半導体ICの生産額がトランジスタを追い越している()。

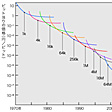

集積回路は、同じチップを多くつくればつくるほど、また、同一チップに集積する素子の数を多くすればするほど、素子当りの単価が下がる。そのもっともよい例が記憶素子(ICメモリー)に現れている。記憶素子の記憶容量に比例するビット当りの価格の年次変化をみると、年次が進んで量産の効果が出ると、ビット単価は確実に下がっている。しかし、同じ集積度のものを生産していては、単価の低下がやがて飽和してくる。したがって、1チップに集積する素子の数を増して、1チップ当りのビット数を4倍にすると、ふたたび単価の引き下げが大幅に可能となる()。

以上のように、年々1ビット単価を確実に下げていくには、数年ごとに集積度の高いICを開発し、1チップに集積する素子数を増して、1チップ当りのビット数を増加する必要がある。1960年以来の製作された記憶素子のチップ当りのビット数の推移をみると、1チップ当りのビット数は1960年から1975年の15年にわたり、年率約2倍の割で増えている。しかし、その後は2年で2倍~3年で4倍と、すこしずつ鈍化している()。

[右高正俊]

動作原理と製法

集積回路で重要な働きをするものは半導体である。とくに半導体ICにおいては、トランジスタから抵抗までのほとんどの回路部品は半導体によってつくる。半導体は、添加する不純物によってn形半導体(電子によって伝導がおこる半導体)とp形半導体(正孔によって伝導がおこる半導体)となり、それぞれ添加する不純物量によって伝導度が変えられる。p形半導体とn形半導体を接して作用させるのがpn接合で、pnpまたはnpnと二つの接合を組み合わせるとバイポーラトランジスタができる。pn接合は、p形半導体側を正極となるようにすると電流がよく流れ、逆にすると電流は流れないので、ダイオードとなる。また逆方向に電圧を加えると電流が流れない状態は、pn接合のp形半導体とn形半導体との間に薄い絶縁物を挟んだ状態と同じことになり、二つの半導体が同一の結晶として連なっているにもかかわらず、電気的には分離されている。半導体ICでは1個の半導体チップの中に多くの回路部品が組み込まれるが、これら部品相互間の分離は、主として以上の方法によっている。薄い絶縁物を半導体で挟んだ状態は、コンデンサーと同じ構造ともなり、逆電圧を加えたpn接合はコンデンサーとして使うこともできる。

バイポーラ半導体集積回路では、高比抵抗のp形半導体を基板として用い、その中にトランジスタ、ダイオード、コンデンサー、抵抗などの回路部品をつくるが、このとき、p形基板と各部品との間には、かならずn形半導体層を介在させ、その層と基板とでできるpn接合で各部品を電気的に分離する。半導体ICでは、回路部品を同時につくるところに特長があり、抵抗もトランジスタも同じ手間でできる。したがって、トランジスタの一部を抵抗、コンデンサー、ダイオードとして使うこともある()。

MOS・ICでは、結晶表面の酸化膜を利用してMOSトランジスタをつくるので、抵抗、コンデンサーも表面につくることが多い。しかし、ダイオードはバイポーラICの場合と同じように、基板内のpn接合を利用する。MOS・ICの回路部品の分離は、酸化膜を使うこともあるが、バイポーラICと同じようにpn接合を使うことも多い()。

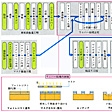

半導体ICは単結晶製造、ウェハー(薄い円盤上の基板)処理などを主要工程とし、さらにマスク製造工程を加え、多くの作業を経てつくられる。単結晶製造工程では、シリコン(ケイ素)の原料である珪石(けいせき)から純粋のシリコンを取り出して単結晶とし、それを切断、研磨して基板のシリコンウェハーとする。ウェハー処理工程では、あらかじめつくられたマスクをウェハーにあわせ、種々の加工を施しパターン形成をしてICチップとする。これを組立て工程で組み立て、配線、封止をし、検査工程を経て、製品として出荷される()。

[右高正俊]

特徴

集積回路の一般的特徴として、小型・軽量で消費電力が小さいことがあげられる。その結果、集積回路を採用すると、応用機器も小型・軽量で低消費電力となり、しかも安価となる。このもっともよい例が電卓である。電卓は1964年ころにはトランジスタ、ダイオードなどの個別半導体を使っていたが、1968年には小規模集積回路(SSI)、中規模集積回路(MSI)を採用するようになり、1970年代にはついに1個の大規模集積回路(LSI)を用いるようになった。そのため1960年代なかばから四半世紀の間に、体積で約4000分の1、重さで870分の1、価格で約700分の1と大幅な進歩を遂げた。この傾向は、その後もいろいろな製品で起こっており、工業製品の高性能化、軽量化、小型化、低価格化に大いに寄与している。

集積回路は各構成素子が小さく、しかも構造的に強固な結晶内につくられ、部品間の配線にはんだ付けなどがないので、振動、衝撃などの機械的外力に強く、信頼度も高い。製造技術の発達によって、集積度が上がってもチップ当りの信頼度は変わらない。MOS・ICに例をとると、内部に含まれる素子数が1970年ごろから2010年の40年間に25万倍と飛躍的に伸びているにもかかわらず、ほとんど信頼度は変わっていない。そのため、各素子当りの信頼性は、年々集積度が上がるにつれて上がる。しかし、熱放散や電流密度の点から、ある程度の面積を必要とする大電力用や、さらには素子の立体的な配置や、構造の最適化が強く要求される超高周波用には、かならずしも有利ではない。また、集積度が上がるにつれて設計に人手がかかるようになる。このことから、設計変更が多く、生産量の少ないものには集積回路は向いていない。

集積回路の特徴を各種のICについてみると、半導体ICは設備投資、開発費が大きいが、集積度、量産性に優れ、集積度、量産性の点ではとくにMOS・ICが優れている。MOS・ICは消費電力も少なく安価で、動作速度も高集積に伴って素子サイズが微細化されるにつれてあがっている。バイポーラICは高速動作ができるが、消費電力が大きい。混成ICは、半導体ICに比べて集積度は大きくできず、量産性も劣るが、設備投資、開発費などもそれほど大きくなく、インダクタンスも組み込めるなどの特長をもっている。また、高周波、高電力のものもつくることができる。ただし、小型化に限界があり、価格もあまり下げられない。

半導体ICに対する設備投資額は、1980年度(昭和55)の通商産業省(当時)の調べでは1210億円で、これは5年前の10倍強であった。さらに、1990年代に入るころには、10倍近くの1兆円を超えた。しかし、1993年(平成5)には5830億円と減少するなど、増減を繰り返しながら2007年(平成19)には過去最大の1兆4965億円まで伸びた。しかしながら、世界景気の後退、日本半導体産業の衰退によって、2009年には、その5分の1以下の2891億円まで下がった。世界市場の景気はその後持ち直しつつあるが、日本国内の伸びはそれほど著しくなっていない。研究投資のほうも同様な傾向を示している。一方、日本の半導体市場の規模は、初期のころは著しい増加を示してきたが、その後は増減を繰り返しながら傾向としては増加を続けている。市場規模が伸びるのは、毎年、より性能の優れた集積回路が社会に出るため、用途が著しい広がりをみせていることによる。高性能のものを安くつくるには、技術革新が必要となり、技術革新のためには、多額の研究投資をして最先端の研究をしなければならない。また、そのような最先端の研究結果を応用して生産を行うには、近代技術の粋を集めた高価な設備をコンピュータで精密制御して使う必要がある。さらに、製造現場の環境や設備にも大きな支出を要しても、最適な状態に整えなければならない。このように、あらゆる分野の最先端知識を駆使した高額な設備と最先端知識を総合して生産するのが半導体ICの大きな特徴となっている。

[右高正俊]

用途

日本における1984年度の実績をみると、総売上高のうち、コンピュータおよびその端末機器が約36%、VTRが14%、音響機器が8.3%、通信機が8%を占めており、その8年前に5分の1強を占めていた電卓は2.5%に下がっている。これは集積回路の用途が一般に広がり、電卓で支えられて伸びてきた日本の特殊性からの脱却を意味する。次に多いものとして、テレビ、事務機、計測制御、時計などがある。とくに注目すべきことは、従来電子機器でなかった時計や自動車などにおいて売上げが増したことである。これは、マイクロコンピュータが発展して、電子機器の自動化、高性能化だけでなく、時計をはじめ自動車、カメラ、ミシン、工作機械などの機械機器の分野でも、電子制御による高性能化が一般化してきたことを意味する。たとえば時計、カメラなどでは、機械部分をICに置き換えることによって高性能化と操作性の向上を図っている。ミシンや工作機械の分野では、自動化、高性能化のほか、コンピュータのプログラムを用いて多様化に対応できる分野を開拓している。2000年代に入ってからの用途別IC需要の傾向として、主としてパソコン用として使われるICの比率が下がり、かわって自動車用が上がっているのが目だつ。自動車では、マイクロコンピュータを用いてエンジンの最適制御と安全性および燃費の向上を進めている。このように、ICの性能が高度化、多様化するにつれて、今後ますます多方面で活用され、便利で快適な社会づくりに役だっていくものと思われる。

[右高正俊]

『電子工学ポケットブック編纂委員会編『電子工学ポケットブック』第3版(1982・オーム社)』▽『伊藤糾次・伊藤容吉著『集積回路基礎技術』(1983・昭晃堂)』▽『右高正俊著『LSIプロセス工学』改訂2版(1988・オーム社)』▽『池田哲夫監修、谷本哲三・常深信彦著『集積回路の基礎と応用』(2001・森北出版)』▽『上西勝三著『わかる集積回路の秘密』(2004・日本理工出版会)』▽『黒木幸令著『学びやすい集積回路工学』(2005・昭晃堂)』

エレクトロニクス部品の生産額推移(日本…

記憶素子(IC)価格の年次推移(日本)…

集積回路チップ当りの素子数の年次推移(…

バイポーラ半導体集積回路の回路部品〔図…

MOS半導体集積回路の回路部品〔図E〕

集積回路の製造工程〔図F〕

化学辞典 第2版 「集積回路」の解説

集積回路

シュウセキカイロ

integrated circuit

略称IC.半導体基板上にトランジスター,ダイオード,コンデンサーなどをつくり,金属配線により集積したもの.個別の部品を配線でつなげた厚膜集積回路と半導体基板上へ各部品をつくり込んだ薄膜集積回路とがあるが,現在,集積回路は後者をさすことがほとんどである.J. KilbyとR. Noyceにより発明され,20世紀最大の発明の一つと称された.この功績により2000年にKilbyはノーベル物理学賞を受けたが,Noyceはすでに他界していた.現在,プレーナー技術とよばれる.半導体表面に写真技術を応用して微細パターンをつくり(フォトリソグラフィーという),これをもとに薄膜の除去や拡散などを繰り返して行い,トランジスターなどのデバイスをつくり込む.集積回路ではトランジスターなどの構造をトータルで微細化する方法で高速化を実現してきた.これはスケーリング則とよばれ,MOS(モス)トランジスターのチャンネル長を1/k倍にすると,チャンネル幅,酸化膜厚や拡散深さなども1/k倍になる考え方である.[別用語参照]LSI

出典 森北出版「化学辞典(第2版)」化学辞典 第2版について 情報

ブリタニカ国際大百科事典 小項目事典 「集積回路」の意味・わかりやすい解説

集積回路

しゅうせきかいろ

integrated circuit

出典 ブリタニカ国際大百科事典 小項目事典ブリタニカ国際大百科事典 小項目事典について 情報

IT用語がわかる辞典 「集積回路」の解説

しゅうせきかいろ【集積回路】

百科事典マイペディア 「集積回路」の意味・わかりやすい解説

集積回路【しゅうせきかいろ】

出典 株式会社平凡社百科事典マイペディアについて 情報

世界大百科事典(旧版)内の集積回路の言及

【記憶装置】より

…また,記憶装置には記憶媒体が交換可能なものとそうでないものとがあり,読出し専用のリードオンリーメモリーもある。

[半導体メモリー]

半導体メモリーとはIC(集積回路の略)を使った記憶装置またはそれを構成するICのことをいう。半導体メモリー用の素子として,1990年頃までは高速性が要求される用途ではバイポーラートランジスターが使われたが,MOSトランジスターが高速になったため,現在では高集積化が容易で消費電力が少ないMOSトランジスターがほとんどの用途に使われている。…

【テキサス・インスツルメンツ[会社]】より

…54年には熱による劣化の激しいゲルマニウムに代えてシリコン(ケイ素)を素材としたシリコントランジスターを初めて開発,4年間にわたるシリコントランジスターからの独占的利益によって経営基盤を強固にした。59年にはTI社のエンジニア,キルビーJack St.Clair Kilby(1923‐ )がIC(集積回路)特許を出願し,IC開発への道を開いた。以後,TI社はフェアチャイルド社と並ぶICの最有力メーカーとして活躍してきた。…

※「集積回路」について言及している用語解説の一部を掲載しています。

出典|株式会社平凡社「世界大百科事典(旧版)」

[名](スル)二つ以上のものが並び立つこと。「立候補者が―する」「―政権」[類語]両立・併存・同居・共存・並立・鼎立ていりつ...